—— 2025 工程实践洞察

适用读者: 硬件工程师、嵌入式开发者、测试/FAE 工程师、产品经理

SEO 关键词: 2025 TDD 噪音、对讲机模块、DMR、EMC/EMI、PSRR、LDO、麦克风偏置、四层 PCB 铺铜工艺、功率电感、语音“嘟嘟声”

摘要(非专业读者亦可理解)

我们的 NiceRF 工程师在调试 DMR 数字对讲机模块的发射模式时,经常会听到“嘟嘟嘟”的低频 TDD 噪音。

许多团队误以为是音频芯片损坏所致,但实际上这并非芯片问题,而是 TDD(时分双工) 模式下收发切换所产生的电流脉动,通过 电源/地回路、PCB 耦合、麦克风偏置电路 等路径“注入”音频链路,最终被“解调”为可听噪声。

本文将结合实践经验,讲解:

- 噪音产生的原理与现象

- 如何快速定位与验证

- 从“加电感”到“四层防干扰布局”的系统化解决思路

- 同时涵盖器件选型、波形分析与设计决策树的要点。

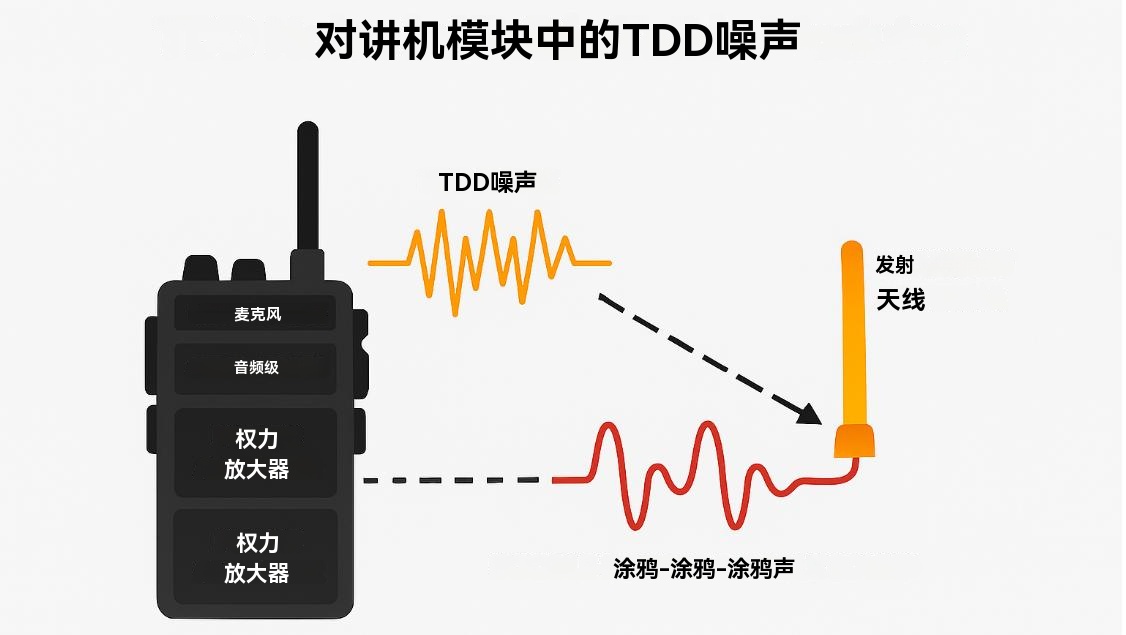

一、什么是 TDD 噪音?(现象与原理)

1.1 现象与根本原因

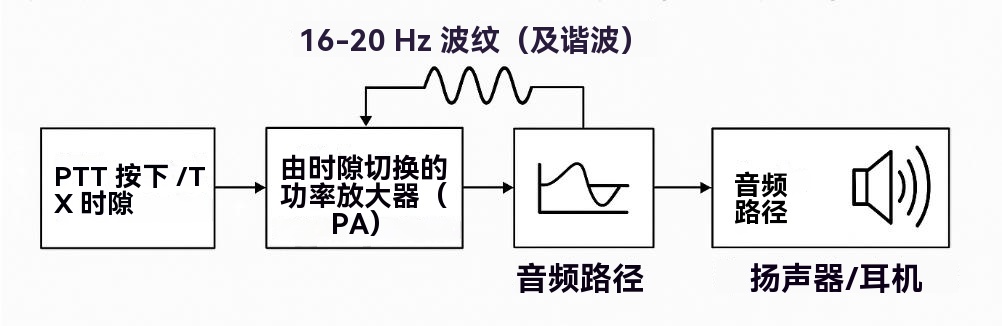

现象: 在按下对讲机 PTT 发射键或发射时隙期间,喇叭或耳机中会出现低频“嘟嘟声”,频率范围在 16–20Hz,带有奇次谐波(10s–100s Hz),听起来类似马达或机枪声。

原因(通俗解释):

在 TDD 模式中,PA(功率放大器)按时隙周期性开关。电流脉动沿着电源和地线传播,耦合到音频部分,被音频电路“解调”为低频包络,从而变成可听噪声。

1.2 工程总结:TDD 噪音传播的三条路径

NiceRF 的设计经验表明,TDD 噪音在工程中主要通过以下三种常见路径传播:

- 电源串扰(PI 问题)

TDD 脉动在电源/地线中引起压降与波动,干扰音频基准电平。 - 布局耦合(EMI 问题)

RF/PA 的大电流回路与 MIC、Audio、Control 线过近,形成电容、电感或共阻抗耦合。 - 滤波不足

麦克风偏置与干净电源(3.3V)隔离度不够,或 LDO 的电源抑制比(PSRR)过低。

提示:

TDD 帧长一般为 60ms,其基波频率约 16.7Hz。频谱上可见的“锯齿状谐波”正是它的谐波梳状谱线。

二、三种“快速止噪”方案 —— 原型阶段即可见效

以下三种方案适用于开发早期或样机验证阶段,无需大规模改板即可验证效果:

2.1 方案 A | 电源输入端 “L + C” 隔离滤波(推荐)

做法:

在模块电源输入串联一个 15 µH、≥1.3 A 的功率电感,并在近端加 100 µF(低 ESR)+ 10 µF + 100 nF 去耦。

作用:

形成低通滤波器,阻断 TDD 低频包络及高频尖峰,抑制“脏电源”进入模块。

2.2 方案 B | 音频/基带独立“干净”3.3V 电源(高 PSRR LDO)

做法:

使用高 PSRR、低噪声 LDO(推荐 XC6228D33 或同等级),在 10Hz–1MHz 范围内保持 >70 dB 抑制比。

作用:

有效隔离输入电源纹波,为音频与麦克风提供稳定偏置。

2.3 方案 C | 麦克风偏置“三段式”滤波 + 地保护

做法:

对麦克风偏置电源使用三级滤波(47 µF + 10 µF + 2.2 µF,钽电容或稳定介质),并在 MIC_V 电压周围铺设连续地铜(地包围 + 过孔栅栏)。

作用:

将噪音包络在偏置端被滤除,麦克风仅“听见”声音信号而非 30V 脉动干扰。

想了解如何在不同 PCB 设计中优化噪音?欢迎联系 NiceRF 工程师团队获取支持!

三、系统级解决方案:电源完整性(PI)与 PCB 工程设计

NiceRF 的测试实践表明,TDD 噪音无法完全通过局部电路“消灭”,

必须从 系统层面 解决电源完整性与 PCB 布局问题。

3.1 电源完整性设计(PI Design)

目标阻抗法:

设计时应满足 $Z_{target} = \Delta V / \Delta I$

例如:若发射瞬态电流变化 $\Delta I = 0.5A$,允许电压波动 $\Delta V = 50mV$,

则 $Z_{target} \le 0.1\ \Omega$。

分频去耦层叠:

- 高频:100 nF,靠近引脚

- 中频:10 µF,布放在中近区域

- 低频:100 µF,放在电源入口

电感选型:

- 饱和电流 ≥ 1.5 × 峰值电流

- DCR 尽量低(典型值 < 100 mΩ)

四、2025 年常见 TDD 噪音问答(FAQ)

Q1:加一个功率电感是否足够?

A:在输入纹波是主因时,这种方案效果明显且易验证。

若噪音还来自 MIC 偏置或布局耦合,则需同时使用高 PSRR LDO + 三段式偏置滤波 + 地包围。

经多项目验证,系统级解决方案 才能从根源抑制噪音。

Q2:为什么加了大电容反而噪音更大?

A:可能引入新的谐振路径或 LDO 稳定性失配。

建议严格遵循器件规格书中的容量与 ESR 窗口,将电容靠近负载端,并检查回路面积,避免形成新的耦合路径。

Q3:为什么两块模块靠近时噪音变大?

A:这是“拍频效应”(Beat Frequency)。

当多块模块以不同步的 TDD 时序工作时,噪音叠加形成拍频。

解决方法包括:

主控同步 TDD 时序,或在物理上增加隔离/屏蔽。

结语

NiceRF 工程团队通过长期研发与验证,总结出一套从 器件选型 → 电源完整性 → PCB 布局 → 系统调试 的完整 TDD 噪音优化方案。若你在 DMR、全双工、音频模块设计中遇到类似噪音问题,欢迎联系我们获取针对性工程支持与设计建议。